Design for In Circuit Testability: Optimizing PCB Layout for ICTAuthor : Colby September 05,sterling silver solder paste for jewelry 2025Table of ContentsIn the world of PCB manufacturing, ensuring that your board can be tested efficiently is just as important as designing for functionality. This is where design for testability ICT(In-Circuit Testing) comes into play. By optimizing your PCB layout for ICT, you can reduce testing costs, improve defect detection, and speed up production. But how do you achieve this? The key lies in strategic planning, such as following test point placement guidelines, ensuring proper ICT probe access, and focusing on minimizing ICT fixture costs. In this comprehensive guide, we’ll walk you through the essential steps and best practices to design a PCB that’s ready for efficient in-circuit testing.

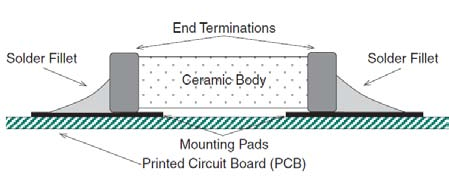

What is In-Circuit Testing (ICT) and Why Does It Matter?In-Circuit Testing, or ICT, is a widely used method in electronics manufacturing to test individual components and connections on a printed circuit board (PCB) without powering up the entire system. It uses a bed-of-nails fixture—a setup with numerous probes that make contact with specific points on the PCB—to check for shorts, opens, and component values like resistance, capacitance, and more. ICT is critical because it helps catch manufacturing defects early, saving time and money in the production process. Designing for ICT isn’t just an afterthought; it’s a proactive approach that can impact up to 25-30% of the total production cost, which is often attributed to testing. A well-thought-out design ensures that testing is faster, more accurate, and less expensive. Let’s dive into how you can optimize your PCB layout to achieve these benefits.

Key Principles of Design for Testability (DFT) in ICTBefore we get into specific layout strategies, it’s important to understand the core principles of design for testability ICT. DFT focuses on making a PCB easier to test by planning ahead during the design phase. Here are the foundational ideas:

With these principles in mind, let’s explore actionable strategies for optimizing your PCB layout for ICT.

1. Test Point Placement Guidelines for Effective ICTOne of the most critical aspects of designing for ICT is following test point placement guidelines. Test points are specific locations on the PCB where probes make contact during testing. Poorly placed test points can lead to incomplete testing or increased fixture costs. Here are some best practices:

2. Optimizing PCB Layout for ICT Probe AccessEnsuring proper ICT probe accessis another cornerstone of a testable PCB design. If probes can’t reach the test points due to component placement or board layout, the testing process becomes inefficient or even impossible. Follow these tips to improve access:

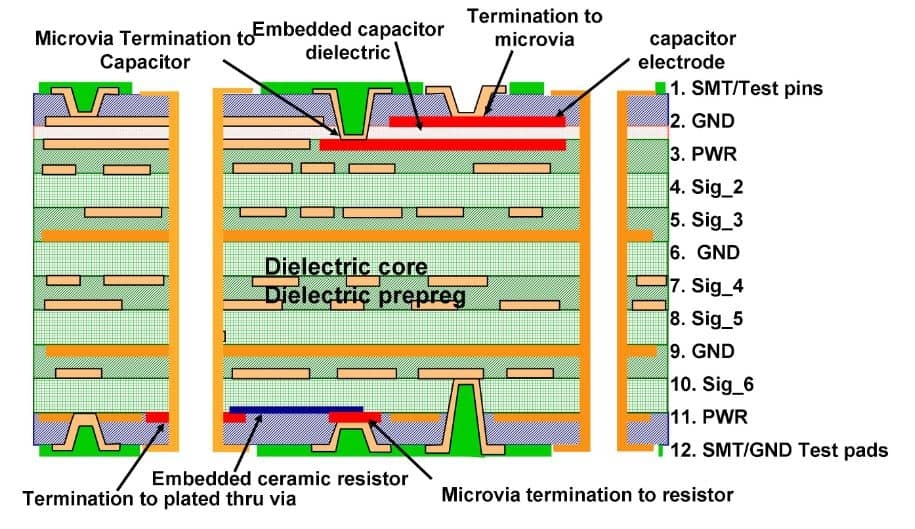

3. Component Placement Strategies for ICT CompatibilityThe way you place components on your PCB can significantly impact its testability. A cluttered or poorly organized layout can hinder probe access and increase testing challenges. Here’s how to optimize component placement for ICT:

By planning component placement early in the design process, you can avoid costly redesigns and ensure a smoother testing phase.

4. Minimizing ICT Fixture Costs Through Smart DesignOne of the biggest expenses in ICT is the cost of the test fixture itself. A bed-of-nails fixture can range from $1,000 to $5,000 or more, depending on the complexity of the PCB. Here are proven strategies for minimizing ICT fixture costs:

5. Addressing Signal Integrity in ICT DesignWhile focusing on testability, don’t overlook signal integrity, especially for high-speed or sensitive circuits. Poor test point placement or excessive probing can introduce noise or affect performance. Consider these points:

Balancing testability with signal integrity ensures that your PCB performs well both during testing and in its final application.

6. Common Mistakes to Avoid in PCB Layout for ICTEven with the best intentions, certain design oversights can undermine ICT effectiveness. Here are common pitfalls and how to avoid them:

By steering clear of these mistakes, you can save time and resources during the testing phase.

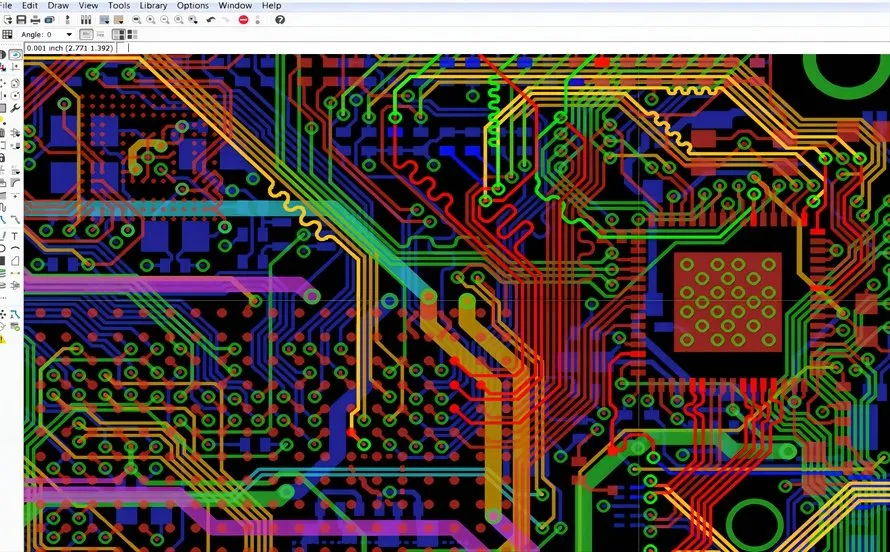

7. Tools and Software for ICT-Friendly PCB DesignModern PCB design software offers features to help with design for testability ICT. While specific tool names vary, look for these capabilities in your design platform:

Using these tools can streamline the process of creating an ICT-ready layout, reducing errors and improving efficiency.

Conclusion: Building Testability Into Your PCB DesignDesigning a PCB with in-circuit testability in mind is a smart investment that pays off in reduced costs, faster production, and higher product quality. By following test point placement guidelines, ensuring proper ICT probe access, and focusing on minimizing ICT fixture costs, you can create a PCB layout for ICTthat meets both manufacturing and testing needs. Remember to prioritize accessibility, balance test coverage with signal integrity, and avoid common design pitfalls. Start incorporating these design for testability ICTstrategies into your next project. With careful planning and attention to detail, you’ll not only streamline the testing process but also deliver reliable, high-quality boards ready for the market. If you’re looking for a trusted partner to bring your ICT-optimized designs to life, our team is here to support you every step of the way. Share · · · · The Role of Flux in PCB Wave Soldering: Selection, Application, and Residue RemovalMarch 16, 2026PCB wave soldering flux types include rosin, water-soluble, and no-clean options with varying activity levels for oxide removal and solder flow. This guide covers selection criteria, spray foam drop-jet application methods, residue removal processes, and alternatives like nitrogen blanketing to boost joint reliability and yields for engineers. Article Achieving Uniform Solder Fillets in PCB Wave Soldering: Process ControlMarch 16, 2026Achieve uniform solder fillets in PCB wave soldering with process control strategies. Optimize flux, preheat, wave height, conveyor speed for consistent fillet shape, height, and wetting balance. Includes visual inspection tips and troubleshooting for reliable through-hole assemblies. Boost quality in production. Article Optimizing Conveyor Speed for Efficient PCB Wave SolderingMarch 16, 2026Learn PCB wave soldering conveyor speed calculation to manage dwell time, immersion depth, and throughput effectively. Electric engineers get practical steps, best practices, and troubleshooting tips for higher process efficiency and fewer defects in wave soldering operations. Article Understanding IPC Standards for PCB Surface Finishes: Ensuring Quality and ComplianceMarch 11, 2026Understand IPC standards IPC 4552 ENIG and IPC 4553 immersion silver for PCB surface finishes. Ensure compliance, enhance solderability, and prevent common defects to achieve reliable, high quality circuit boards. Article Miniaturization Challenges in PCB AssemblyMarch 11, 2026Navigate the complexities of high density interconnect PCB assembly and precise component placement. Learn to tackle miniaturization challenges, from tiny part handling to thermal stress, ensuring robust and reliable electronics. Article High Speed Routing Techniques: PCBMarch 11, 2026Master high speed routing in PCBs to ensure signal integrity and minimize electromagnetic interference. Learn essential techniques for robust designs, from controlled impedance to differential pair strategies. Prevent performance issues and achieve reliable electronics. ArticleGet Instant PCB |